Synopsys: Harnessing Complexity

You can listen to this Deep Dive here

Chip design has long been a paradoxical craft. On one hand, engineers must trust sophisticated software to help them craft circuits of mind-boggling complexity; on the other, they maintain a healthy skepticism, knowing a single flaw can doom a chip. The old mantra "trust, but verify" could well have been coined for this process. Hardly any company embodies this delicate balance between automation and human oversight better than Synopsys, a company that was founded just three months prior to TSMC in the mid-1980s as a scrappy spin-off from General Electric (GE). Yes, this was Jack Welch’s GE which apparently spread its tentacles even into semiconductors.

Synopsys’s origin story unfolds amid a turning point in semiconductor history. In 1985, a severe industry downturn prompted GE to pull back from its semiconductor venture, leaving a small team of engineers led by Dr. Aart de Geus at a crossroads. They had developed an innovative logic synthesis tool, a software capable of taking a high-level description of a digital circuit and automatically generating the intricate logic gates to implement it.

At the time, this was revolutionary. Chip designers were used to managing that task manually, drawing out circuits gate by gate. Indeed, to create a schematic in the mid-1980s, an engineer would often hand-draw everything i.e. every logic gate, resistor, and connection on vellum paper since computer schematic tools were not yet available. This laborious process could take weeks or months for a complex circuit, with frequent re-drafts and “cut-and-paste” edits done by literal scissors and tape. The Synopsys founding team envisioned a better way.

In 1986, they spun out of GE (with the company’s blessing and even a modest technology license), forming a startup originally named Optimal Solutions. By the following year, they had relocated to Silicon Valley, aptly renaming the venture Synopsys (short for synthesis and optimization systems) and setting out to commercialize their new method of chip design.

For decades, chip designers viewed their work as equal parts engineering and art. The thought of ceding the “artistic” control to a software program met with natural resistance. In the early years, letting a tool automatically modify a circuit was almost taboo. On the Acquired podcast, Aart de Geus (founder of Synopsys), and Sassine Ghazi (the current CEO of Synopsys) recollected some of those early days. They half-jokingly referred to their synthesis engine as having a “license to kill,” because giving a tool free rein to alter a circuit design felt as dangerous as it sounds. Many engineers were simply uncomfortable with software intervening in what they saw as their creative process. “Please only aid me, do not automate for me,” was a common sentiment among chip architects of the time. Underneath this reluctance was a deep issue of trust: designers weren’t convinced that an algorithm could make better decisions than an experienced human, and they worried that automated changes might introduce hidden bugs. This cultural skepticism meant that Synopsys not only had to invent the technology, but also persuade an entire industry to believe in it.

What problem was Synopsys solving at inception? In a word: complexity.

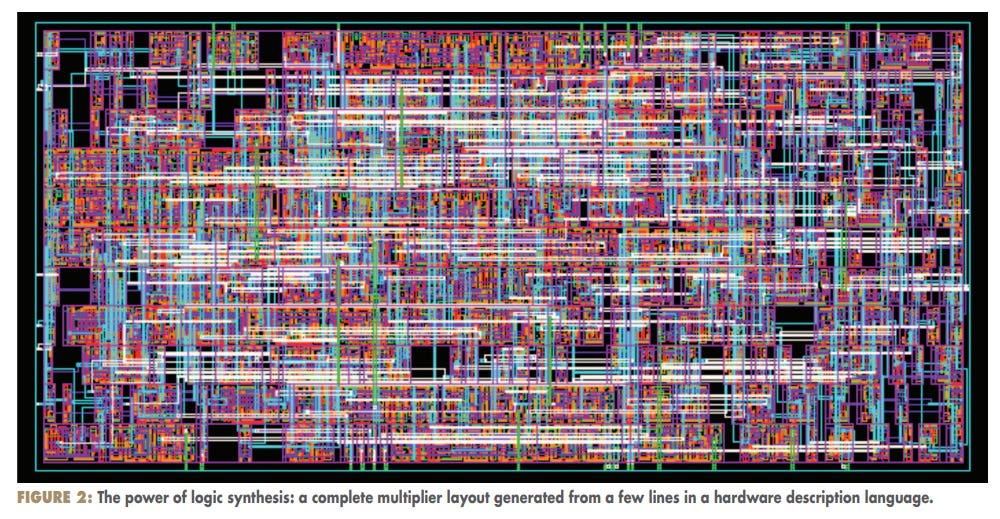

The mid-1980s marked the dawn of an era when microchips were growing so intricate that traditional design methods were reaching a breaking point. Each new chip generation packed in more transistors than the last, making the schematics exponentially harder to manage. Synopsys’s breakthrough was to transition chip design “from schematic to language-based” representation. Instead of physically drawing every gate, a designer could write code (in a hardware description language) describing the chip’s behavior, and Synopsys’s software, their flagship Design Compiler introduced in 1987, would automatically synthesize that code into an optimized gate-level implementation. This logic synthesis automation was like a compiler for hardware, translating abstract designs into silicon-ready blueprints. It drastically accelerated design work and reduced human error, at a time when such a leap was desperately needed. Just take a look at the diagram below and you may appreciate why humans may not be best suited to draw something like this by hand.

Even though there was skepticism initially, those who tried the tool found that it could shave months off design cycles by handling the grunt work of logic gate optimization. One by one, major semiconductor companies gave this new approach a chance. The results spoke for themselves: chips reached timing goals and functioned correctly, even when much of the design had been generated by Synopsys’s algorithms. By the early 1990s, Synopsys had established relationships with virtually all of the world’s leading chipmakers. The young startup expanded its portfolio beyond synthesis, adding simulators for testing chip behavior, timing analyzers to ensure speed targets, and other tools to round out a complete design suite.

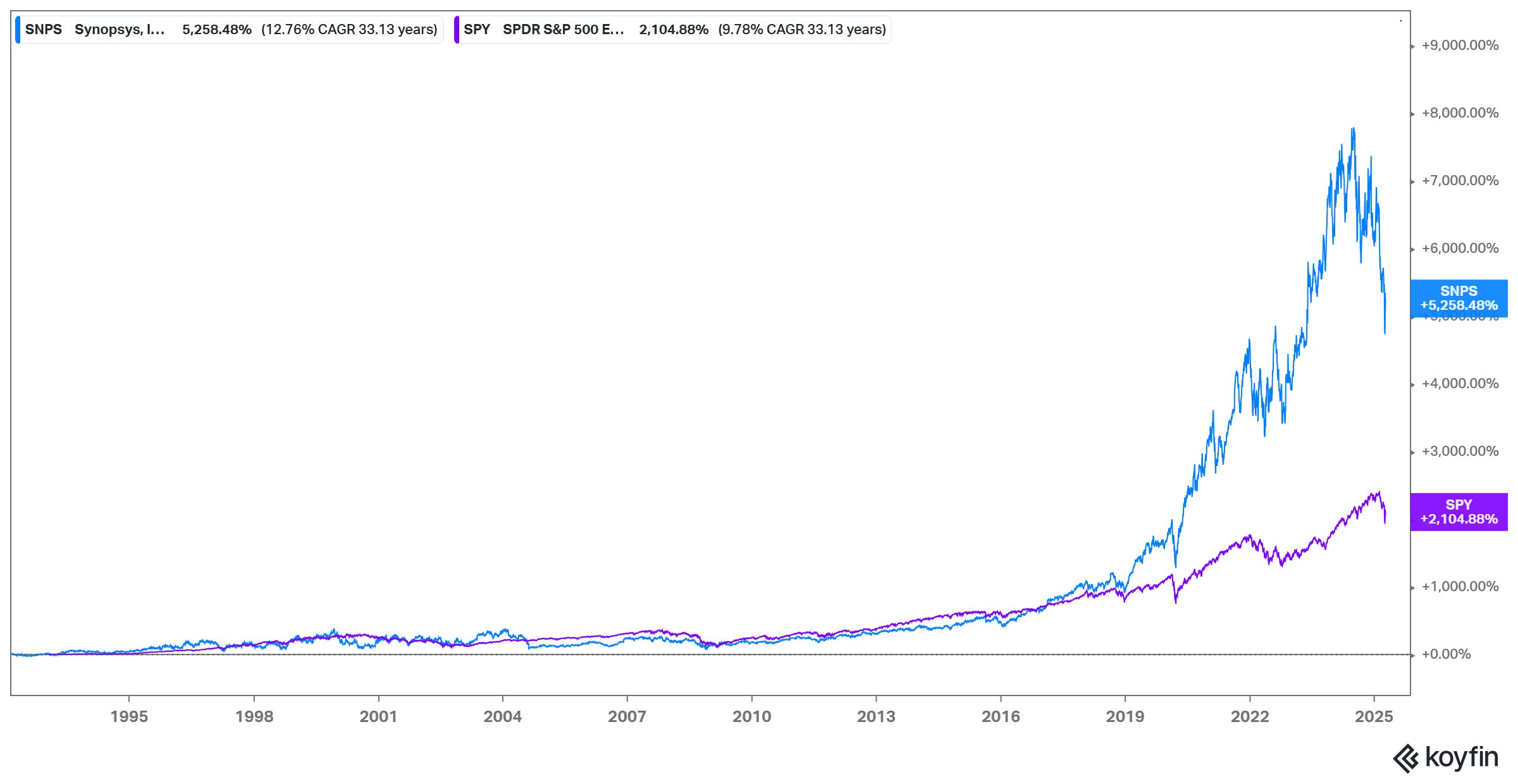

Synopsys grew rapidly on this acceptance. In fact, the company’s momentum carried it to an IPO in 1992, barely six years after its founding, a testament to the value it was delivering to chip designers desperate for solutions. In the year it IPO-ed, Synopsys posted ~$92 million revenue and ~$8 million operating profit. By the end of the 1990s, Synopsys reached $806 Million revenue and $251 Million operating profit. Of course, tech bubble crashed afterwards and the stock experienced ~60% drawdown in 2000. The stock fully recovered in just four years but then experienced another ~60% drawdown. Like many tech companies, Synopsys eventually took more than a decade to decisively exceed its peak during tech bubble! Despite these rise and fall, Synopsys is more than a ~50-bagger since its IPO in 1992.

Today, Synopsys stands as a linchpin of the semiconductor ecosystem. A company that was born from a risky idea that software could design hardware is now entrenched as a trusted ally in virtually every advanced chip project. The introduction of automated design tools fundamentally changed the economics and timeline of chip development. To understand and appreciate their current role in the broader semiconductor value chain, let me provide you a more granular understanding of their current business.

While it is not essential, I would like to note that if you’re largely unfamiliar with semiconductor industry, it may be more helpful to start with my semiconductor primer first and then read this Deep Dive.

In section 1, I will go deep to Synopsys’ current business, economics, and growth drivers for both of its two segments: design automation, and design IP.

In section 2, I expanded on Synopsys’ potential acquisition of Ansys. Then in section 3, I looked into the moats of Synopsys as well as the competitive dynamics between Cadence and Synopsys. In section 4, I will show what is likely currently embedded into the stock price. Finally, I will offer some concluding thoughts and disclose my overall portfolio. Subscribe to keep reading!